掃碼添加微信����,獲取更多半導(dǎo)體相關(guān)資料

摘要

? ? ? WL-CSP是一種低調(diào)的����、真正的芯片尺寸封裝,完全建立在使用前端和后端處理的晶圓上�����。使用光電介質(zhì)和再分布金屬將管芯的外圍焊盤(pán)重新分布到區(qū)域陣列中��,消除了對(duì)襯底或插入物的需要��。焊球被放置在重新分布的金屬焊盤(pán)上并回流����,形成一個(gè)大的間隙�����,提高了可靠性���。通過(guò)仿真優(yōu)化了試驗(yàn)車(chē)輛的保險(xiǎn)杠結(jié)構(gòu)和襯墊幾何形狀,并進(jìn)行了試驗(yàn)驗(yàn)證�。這種WL-CSP技術(shù)是使用一個(gè)5×5 mm2的芯片和0.5 mm間距的8×8焊料凸塊陣列進(jìn)行評(píng)估的。使用1.2毫米厚的2層FR-4板進(jìn)行板級(jí)可靠性測(cè)試��,該板具有涂有OSP的0.25毫米非阻焊劑限定的銅墊����。標(biāo)準(zhǔn)厚度的WL-CSP晶圓片為27密耳。進(jìn)行評(píng)估以評(píng)估通過(guò)減薄晶片來(lái)提高WL-CSPs的潛在可靠性����。使用兩種技術(shù)將晶片減薄至4密耳厚。第一種方法是標(biāo)準(zhǔn)晶圓背面研磨�����。第二種是等離子體蝕刻的新方法���,它產(chǎn)生無(wú)損傷的表面并提高晶片和管芯的強(qiáng)度����。將通過(guò)比較標(biāo)準(zhǔn)WL-CSP和使用上述技術(shù)減薄的CSP來(lái)介紹板級(jí)可靠性。

?

介紹

? ? ? 隨著電子元件的尺寸不斷縮小�����,半導(dǎo)體行業(yè)正朝著集成電路小型化的方向發(fā)展���。晶圓級(jí)芯片級(jí)封裝(WL-CSP)正在成為封裝中低輸入輸出設(shè)備的一種流行方法。WLCSP性價(jià)比高���,易于測(cè)試�,占地面積小����,外形低調(diào)。

?

晶圓減薄

? ? ? 晶圓減薄可以分為機(jī)械背面研磨和等離子體蝕刻����。機(jī)械研磨中,使用兩步工藝從晶片背面去除不需要的硅——先粗磨�����,再細(xì)磨。等離子體刻蝕是一種利用大氣下游等離子體(ADP)的干法刻蝕技術(shù)��。使用這種方法���,可以均勻地減薄晶片�����,而不會(huì)產(chǎn)生微裂紋或損壞硅晶格����?���?梢栽跈C(jī)械研磨之后使用等離子體蝕刻來(lái)幫助去除工藝過(guò)程中產(chǎn)生的表面缺陷。

?

電路板級(jí)可靠性

? ??

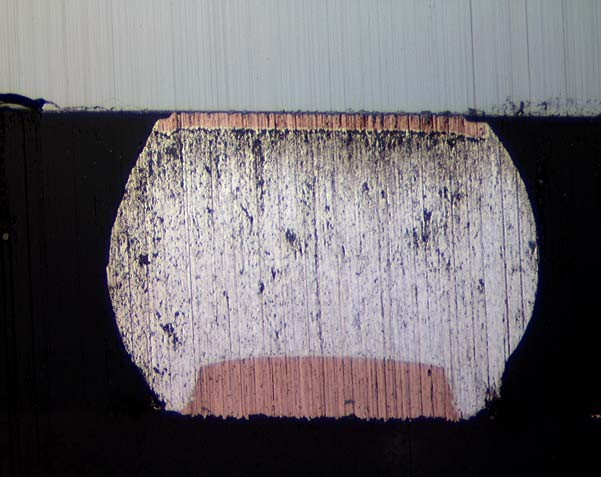

圖5:連接于電路板上的WLCSP的典型橫截面

結(jié)論

? ? ? 晶圓級(jí)封裝技術(shù)通過(guò)消除襯底和底部填充簡(jiǎn)化了工藝并降低了成本�����。使用預(yù)制球?qū)е麓蟮恼w塌陷高度�,這滿足商業(yè)應(yīng)用的焊點(diǎn)可靠性要求。通過(guò)增加使用變薄的晶片�,可靠性得到了提高。通過(guò)兩種減薄方法的比較,在每種情況下使用小樣本量���,與標(biāo)準(zhǔn)研磨技術(shù)相比���,等離子減薄的使用似乎賦予了額外的可靠性。此外���,薄化晶片將失效模式從管芯側(cè)的焊料開(kāi)裂轉(zhuǎn)變?yōu)榘鍌?cè)的焊料開(kāi)裂�。

?

文章全部詳情�����,請(qǐng)加華林科納V了解:壹叁叁伍捌零陸肆叁叁叁