掃碼添加微信����,獲取更多半導體相關資料

引言

? ? ? 清潔是半導體集成電路生產過程中經常反復出現(xiàn)的一個過程步驟����。它既可以從前一個過程中去除殘留物��,也可以為下一個過程準備表面�。清潔和薄膜沉積過程的集成是至關重要的�。氫氟酸最后一次清洗過程后的沉積延遲會導致環(huán)境暴露下裸硅表面的氧化物再生,或僅僅是表面的再污染����。這將導致生長模式的改變或薄膜質量的惡化,并最終導致設備性能或生產的下降��。

?

實驗

? ? ? 這項研究使用了導體蝕刻室�、電介質蝕刻室、微波剝離室和濕式清潔室的集群工具��。清潔室基于Lam的受限化學清潔技術���,使用清潔頭以高流量流體流掃描晶圓表面�����,確保持續(xù)的化學物質補充和快速的副產品去除���。清潔過程的暴露時間約為1秒�。

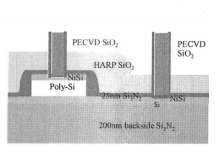

? ? ? 對于接觸應用����,圖1使用了65納米節(jié)點兼容的短回路流程,該流程由用于柵極疊層��、隔離物和NiSi的標準工藝模塊組成����。最小尺寸為90納米的接觸孔在25納米PECVD氮化物/90納米高縱橫比工藝HARP氧化物/200納米PECVD氧化物的疊層上用“193納米浸沒光致抗蝕劑”構圖。使用CO/O2/C4F6/CH2F2氧化物蝕刻和N2/CHF3 Si3N2開口的等離子體工藝順序蝕刻晶片��,隨后是CF4/O2/N2微波帶���。隨后���,用不同的化學溶液清洗晶片,并研究干蝕刻/剝離和濕清洗之間的延遲時間對清洗效率的影響���。用于清潔的化學溶液是去離子水DIW�、稀釋的氫氟酸HF,在DIW通常為1重量%�,或氫氧化銨NH4OH-過氧化氫H2O2混合物APM,通常比例為1份29重量% NH4OH對5份30重量% H2O2對18份DIW 1:5:18.工藝流程為完成接觸金屬化物理氣相沉積TaN/Ta阻擋層和電化學沉積銅以及基于銅/Aurora LK的單鑲嵌模塊��。

?

圖1 用于接觸應用的疊層結構

? ? ? 掃描電子顯微鏡掃描電子顯微鏡照片是以自上而下的方向拍攝的��。該工具配備了柱后Gatan成像過濾器tridiem-GIF�,帶有能量色散x射線分光鏡EDAX和STEM裝置。透射電鏡樣品取向為硅襯底的110°晶向平行于電子束����。熱解吸質譜在快速熱處理器-大氣壓電離質譜儀室中進行��,并結合VG的微量分析��。

?

結果和討論

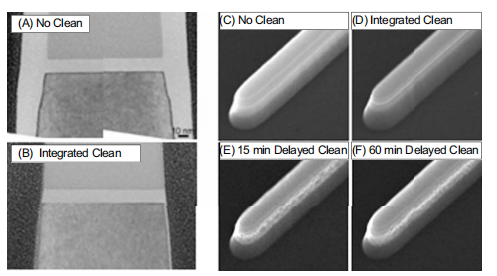

? ? ? 淺溝槽隔離刻蝕延遲效應的觀察�。在干法蝕刻和剝離淺溝槽隔離結構之后,不同厚度的殘留物出現(xiàn)在溝槽側壁上����,如透射電鏡和掃描電鏡圖所觀察到的。圖2A和2C��,在含Cl2/O2的等離子體中產生的這些殘留物是氯化氧化硅9���,通常在蝕刻過程中用作側壁鈍化層���,以獲得所需的溝槽錐度����。在68℃下�,使用1%的氟化氫,曝光時間為2秒���,蝕刻后殘留物可立即清洗���。圖2B和2D,沒有觀察到墊氧化物的橫向侵蝕��。移除的能力使用相同清潔工藝的這些殘留物隨著蝕刻和清潔之間的延遲時間的增加而減少�����。1小時的延遲時間����。與半導體制造中的正常排隊時間相比,2F對清潔性能有很大影響����,因此殘留物沒有完全去除���。在短至15分鐘的延遲時間內觀察到這種效果。圖2E橢偏光譜也應用于這些樣品���,并提供了側壁殘留物厚度的半定量分析����。未示出的結果證實了掃描電鏡的觀察結果:用15分鐘的延遲時間清洗的結構產生的清潔度水平介于原始“非清潔”結構和蝕刻延遲時間后立即清洗的“集成清潔”結構之間��,大約為1分鐘�。

?

圖2 利用TEMA和B、SEMC和F1%HF評估STI結構腐蝕后殘留物去除和底物損失的腐蝕清潔延遲時間����,2s暴露時間

? ? ? 多晶硅柵刻蝕延遲效應的觀察���。通過將基于TEOS硬掩膜的聚硅門蝕刻過程從硬掩膜和聚硅蝕刻步驟之間的光刻膠帶步驟移動到完整的蝕刻過程的結束�,被有意失諧以產生可見的殘基����。這導致了光刻抗蝕劑側壁上殘基的堆積���,在過程序列結束的步驟中坍塌在結構的頂部。蝕刻后殘留物在使用1%的氟化氫在68℃下蝕刻后立即可清洗���,清洗暴露時間為2秒�����,這導致0.6納米的氧化物損失����。相比之下�����,使用相同的清洗工藝去除這些殘留物的能力隨著蝕刻和濕法清洗步驟之間的延遲增加而降低�����。1小時的延遲時間�,與典型的fab排隊時間相當,顯示出對殘渣去除的容易性有顯著影響�。

? ? ? 淺溝槽隔離和多晶硅柵刻蝕的延遲效應機制。使用氯氣/O2和氯氣/HBr/O2等離子體蝕刻硅基底�����,如用于STI和聚硅門蝕刻應用,會在工藝室的側壁和器件結構上產生類似sioxcly的殘基���。通常存在一個成分梯度:表面層更富Cl���、H和br,而體積層被氧化得更多���。殘渣層可以通過隨后暴露于含o2的等離子體而深度氧化�,如本研究中使用的干條帶被氧化�,在氧化物殘留物中只留下微量的鹵素。這種組合物解釋了為什么蝕刻后的殘留物很容易通過干燥蝕刻條帶過程之后的高頻濕清潔步驟去除��。

? ? ? 作為延遲接觸后蝕刻清潔的結果�,觀察到的電性能和相關產量的損失是一個重要的發(fā)現(xiàn)。使用先進的物理表征方法TEM�����、EDAX和EELS進一步研究了這種延遲時間效應的起源��。對于“不清潔”和“28小時延遲清潔”的樣品�,在金屬屏障/NiSi界面處明顯檢測到氧氣。相比之下����,對于具有集成清潔的樣品,沒有發(fā)現(xiàn)含氧的界面層�。應該注意的是,這些含氧殘留物不能通過隨后的阻擋層沉積工藝的氬濺射預清洗來去除�����。該氧化物層最有可能在干法蝕刻和干法剝離過程中形成�����,并且很容易在蝕刻或剝離過程之后立即通過濕法清洗去除�����。與前面討論的二氧化硅蝕刻后殘留物的機理類似�,含氧化物殘留物很可能在暴露于潔凈室環(huán)境期間老化和強化,使得它們更難通過濕法清洗或濺射清洗工藝去除���。

?

總結

? ? ? 我們已經觀察到由于干法蝕刻和濕法清潔工藝步驟之間的延遲造成的負面影響���。使用相同的濕法清洗工藝去除蝕刻后殘留物的能力隨著蝕刻和清洗之間延遲時間的增加而降低����。對于STI應用��,觀察到導致清潔效率降低的最短蝕刻清潔延遲時間為15分鐘��。對于多晶硅柵極和接觸應用��,延遲1小時后清洗性能下降���,與半導體制造中的典型排隊時間相當�����。在接觸層面�,觀察到對電性能的有害影響:干法蝕刻/剝離和濕法清潔之間的1小時延遲時間導致接觸電阻增加高達30%����,產量損失高達25%。

? ? ? 使用更強的清洗條件是去除殘留的淺溝槽隔離和多晶硅柵極或恢復電性能接觸的一種方法�。對于STI和聚硅柵的應用,這是通過使用更高的高頻濃度或更長的時間來評估的���。結果發(fā)現(xiàn)����,在相同的凈清潔暴露濃度和時間下�����,更短的化學清潔優(yōu)于更長的清潔與更稀的化學�����。對于接觸應用����,通過從apm-切換到基于hf的清潔化學,獲得了更具侵略性的條件���,這成功地克服了延遲時間效應��。然而���,對于所有的應用,使用更積極的殘留物去除過程來避免延遲效應是以犧牲更高的基底損失為代價的��,這通常是不可取的。

? ? ? 干法蝕刻和濕法清洗工藝的集成可以增加工藝余量:對于相同的清洗條件�,集成的蝕刻清洗序列比干法蝕刻和濕法清洗之間具有延遲時間的序列更穩(wěn)健?��;蛘?�,集成的蝕刻-清潔順序能夠使用寬松的清潔條件���,以低襯底損耗實現(xiàn)良好的殘留物去除。