掃碼添加微信�,獲取更多半導體相關資料

晶體管的整體質量是金屬氧化物半導體的主要問題之一,本文主要研究柵氧化層��,在金屬氧化物半導體晶體管中����,包括對其質量的全面討論,為了充分理解影響回顧了柵氧化層的晶體管結構�,觀察其性能的操作取決于其柵極氧化物的質量。

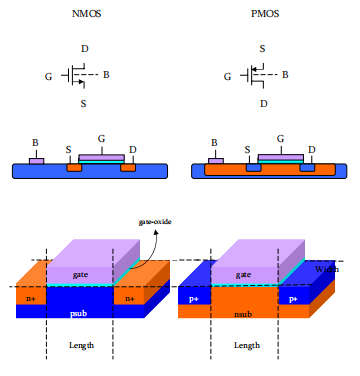

MOS晶體管是通過半導體分層過程產(chǎn)生的電壓控制電流源�。下面的圖1顯示了NMOS和PMOS設備的簡化版本以及相應的電路表示�����,在結構上,晶體管由n型或p型(分別摻雜磷或硼)的大塊硅襯底組成��,連接方式為B��,生長柵極氧化物絕緣層以將連接G的多晶硅柵極與基底材料隔離����,最后將n或p型硅的兩個植入?yún)^(qū)域分別創(chuàng)建源區(qū)和漏區(qū),連接S和D��。

?

?

圖1

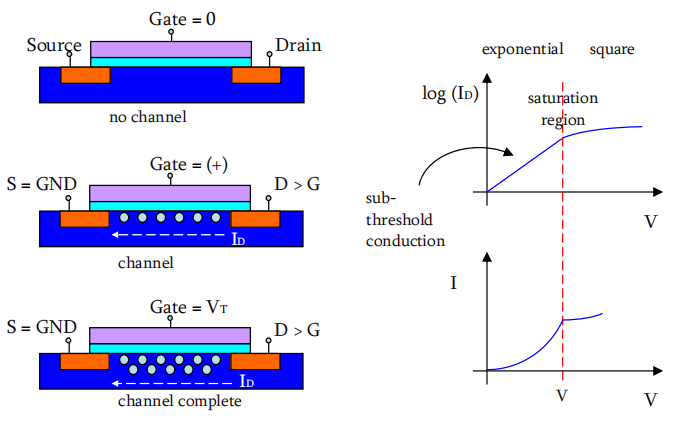

晶體管工作的基本原理非常簡單����,NMOS正電壓應用到門,這開始畫少數(shù)載體�,即電子,門基板接口�,施加到漏極的正電壓(源極接地)將電子從源極掃描到漏極,產(chǎn)生電流���,這是金屬氧化物半導體工作中感興趣的基本電流�。下面的圖2說明了這一點���。

?

圖2

圖2是處于飽和狀態(tài)下的MOS(典型的使用區(qū)域)����,在這種情況下,漏極電位總是高于或等于柵極電位����,從圖中我們可以看到,ID首先呈指數(shù)增長���,然后是平方增長��,正是在這個過渡點上����,晶體管被認為是“開”的�。此時的柵極電壓被認為是閾值電壓VT,可以清楚地看到柵極氧化物絕緣性質的重要性����。理論上,通過氧化物的電位從基板中吸引載流子����,在源極和漏極之間創(chuàng)建一個傳導路徑,而沒有電流流入柵極,然而��,在現(xiàn)實中����,如果氧化物中存在缺陷��,電流會開始迅速增長���,需要有一套標準來確定柵極氧化物的質量及其成為完美絕緣體的潛力����。

??

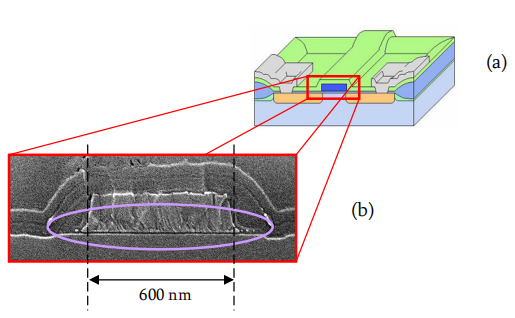

圖3

下面的圖3(a)顯示了一個更詳細的晶體管的三維圖像����,使用一個實際的掃描電子顯微鏡,SEM(b)��,更仔細地觀察柵極區(qū)域���,柵氧化物是用紫色圈出的非常細的黑線�����,柵極聚硅是在這條黑線上方形成的較淺的矩形��,可以看到有效通道長度600納米和柵極厚度12.2納米之間的巨大尺度差異�。

從上面可以看到,巨大的物理長度電流必須在晶體管中流動�����,而極薄的氧化層試圖包含電流單獨流向基板�,而不是進入柵極,如此薄層材料中的任何小缺陷都可能對晶體管的質量造成災難性的影響����,應該包括對氧化物的電荷到擊穿的完整表征。

如上所述���,最終沒有產(chǎn)生任何顯著差異�,大大提高了氧化物擊穿值��,并已作為永久標準工藝實施�����,在試驗材料上的新汞冷啟動工藝優(yōu)于標準氧化物擊穿�����,但在生產(chǎn)材料上的結果不同。因此��,PRE-GATE步驟將沒有任何永久的修復���,雖然長期的表征和耗時的測試顯示了對測試波動的改進,但本文表明����,所獲得的結果不一定能很好地轉移到大規(guī)模生產(chǎn)車間,也不能反映在第二次測試的部分結果中

利用多種形式的應力測試�,對一種12.2納米的門氧化物進行了討論和完整的表征,討論了一種具有12.2納米門氧化物的多點測試載體�����,并進行了完整的表征���,此外在兩個獨立的清洗機器中分析了預柵極氧化物沉積硅的清洗步驟�����,并對幾種新工藝進行了初步的評估和表征��。不幸的是��,最終的分裂沒有顯示出生產(chǎn)材料的分解性能改善��,然而����,這項工作將作為任何想要改進或描述晶體管柵氧化物的工程師來說,作為一個極好的起點�,因為它提供了比生產(chǎn)測試更詳細的測試結果。